mathjax

2018-11-29

KiCad, Generalization and Workflow

ugh the preceding document is the culmination of a set of rants and thought about PCB design software for some; there's a TLDR at the bottom. I ran out of steam writing it eventually but some of the ideas with work flow are kind of interesting. I'm going to post the bulk of it on kicad forums to see if anything will come of it there. If it doesn't maybe it's time to take a stab at the kicad source.

Labels:

kicad

2017-07-11

Spiral Multiplier Nixie Clock

First I would like to devote this post to all the engineers that put their time into the creation of the modern printed circuit board and namely Pail Eisler who apparently is the inventor. Because I decided to point to point solder this project together and I am never doing that again, even if it is 'small' and all through hole, just like this dumb clock . When a 40 pin fan out is required there are just so many connections involved, stripping every wire, hand soldering each joint. I did this originally because I wasn't in the mood to route and wait for a board, that was a horrible idea. Boards get routed by hand threading wires and soldering them in place or they get routed on a computer; one method is infinitely more painful for a even a moderate number of components.

The clock is a bit of a Rubegoldberg machine but really it didn't have to be this way. All of the pain and annoyance of this particular project are entirely self inflicted, but once everything was debugged everything seemed to work as intended and nothing exploded of it's own accord. I helped it out with that a few times though.

That being said I've made a nixie clock. It powers the tubes from a spiral multiplier topology; if you're wondering what that is, see my last post cause I made it up and haven't seen it anywhere else. In this particular case it is a 4s3p multiplier array. This one in particular has 3 strands in parallel because it was easy to make a ring oscillator to drive them all out of phase, there is no other particular reason for it. Future designs could be done in a much more efficient compact fashion, that being said despite being an overly complex machine, it works. The FETs don't get hot at all, the caps are stressed a lot voltage wise but that was somewhat intentional and a bit of an experiment and you wouldn't notice if any of the supply was actually turned on and there's no noticeable noise, really nothing is being worked hard power wise.

The build up of the system went in a piece wise fashion. Multiplier was built up first, mainly because it was easy to free hand and capable of being treated as an independent lump with only a few connections.

This assembly really was the painful part. The speed of bending each wire into joint and soldering it was excruciating.

After making the multiplier came the PWM /controls set up. Since the system is open loop so there really aren't any controls to speak of. Controls would be logical for almost any other implementation, however the input to the multiplier system is a 15V regulated wall wart, and the multiplier itself is effectively a fancy step-up with constant load. So load variation and line variation are not issues. If people had the potential to plug in other regulators, or if the system were powered straight from the line regulation would be more of a concern. After finishing the inverter some basic testing was possible:

The multiplier is hiding in the far right f this picture, the inverter is front and center. Controls/ inverter are dead center. The Red wire is the HV into the tube. Output voltage from the supply can reach >200V with no load, but rides at 170V under load with all of the nixies. The voltage over the tube (that's on the multimeter) sits right at where the data sheets says it should site ~140V and in this test there was a resistor doing the current limiting for the tube. There are probably some resonant effects playing into the output voltage stability that I haven't characterized. The system output voltage is surprisingly invariant under different loads.

Feed back can always be added but, it wasn't needed and time, cost, effort...laziness efficiency. The heart of the 'controls' is a 3-inverter ring oscillator. It generates three 120 degree out of phase triangle waves. These go to the inputs of three comparators that output three square waves. AND THEN they go to a set of inverters that flip half the PWM signals, add dead time then buffer the outputs. This was all done using 74XX14's and passives/diodes, too many of them. Really the more proper way to implement this set up effort would be a PLD or microcontroller, it would greatly reduce parts count and over all cost of this endeavor; since only one of this particular object was getting made and didn't want to futz with tool chains and microcontrollers. It seemed like less trouble to do it in a very brain dead way using 74 logic with this circuit:

Six of these circuits were used, one for each pwm channel. They invert each wave and lop off the front of each pulse. Half of the delayed signals are inverted again. This makes it so there will be dead time between each pwming pair; and no shoot through between the hi and lo switches in each bridge.

The duty cycle is constant around 50% and the system is run approximately resonantly at 47ish kHz.

The clock is a bit of a Rubegoldberg machine but really it didn't have to be this way. All of the pain and annoyance of this particular project are entirely self inflicted, but once everything was debugged everything seemed to work as intended and nothing exploded of it's own accord. I helped it out with that a few times though.

That being said I've made a nixie clock. It powers the tubes from a spiral multiplier topology; if you're wondering what that is, see my last post cause I made it up and haven't seen it anywhere else. In this particular case it is a 4s3p multiplier array. This one in particular has 3 strands in parallel because it was easy to make a ring oscillator to drive them all out of phase, there is no other particular reason for it. Future designs could be done in a much more efficient compact fashion, that being said despite being an overly complex machine, it works. The FETs don't get hot at all, the caps are stressed a lot voltage wise but that was somewhat intentional and a bit of an experiment and you wouldn't notice if any of the supply was actually turned on and there's no noticeable noise, really nothing is being worked hard power wise.

The build up of the system went in a piece wise fashion. Multiplier was built up first, mainly because it was easy to free hand and capable of being treated as an independent lump with only a few connections.

|

| First, assembly of the multiplier stack |

|

| then the controllllls and inverter |

|

| mooore soooooldering controls and inverter |

After making the multiplier came the PWM /controls set up. Since the system is open loop so there really aren't any controls to speak of. Controls would be logical for almost any other implementation, however the input to the multiplier system is a 15V regulated wall wart, and the multiplier itself is effectively a fancy step-up with constant load. So load variation and line variation are not issues. If people had the potential to plug in other regulators, or if the system were powered straight from the line regulation would be more of a concern. After finishing the inverter some basic testing was possible:

|

| Single tube test of multiplier |

The multiplier is hiding in the far right f this picture, the inverter is front and center. Controls/ inverter are dead center. The Red wire is the HV into the tube. Output voltage from the supply can reach >200V with no load, but rides at 170V under load with all of the nixies. The voltage over the tube (that's on the multimeter) sits right at where the data sheets says it should site ~140V and in this test there was a resistor doing the current limiting for the tube. There are probably some resonant effects playing into the output voltage stability that I haven't characterized. The system output voltage is surprisingly invariant under different loads.

Feed back can always be added but, it wasn't needed and time, cost, effort...

|

| It nibbles off the front end of the wave form and inverts it |

Six of these circuits were used, one for each pwm channel. They invert each wave and lop off the front of each pulse. Half of the delayed signals are inverted again. This makes it so there will be dead time between each pwming pair; and no shoot through between the hi and lo switches in each bridge.

|

| Example of dead-time between falling and rising wave forms there is indeed something weird with the upperr wave form but I can't actually remember what is was anymore. |

|

| Pretty Glowy Tubes |

The real regrets in this project (besides the assembly) comes with implementation of the digital controls for the clock. The power electronics were really the less obnoxious part, maybe that says something about my skill set, but at least I know why this part of the implementation was stupid and had an initial reason for the subsequent masochism. The digital controls comprises a clock chip, microcontroller, and load of stupid that fans out the microcontroller to all of the HV outputs. The clock chip is one of the cheapest through hole clock chips available the DS1307 by maxim. It's a pretty simple object and uses I2C to communicate with the microcontroller, this helps it keep actual accurate time with a crystal. One thing to note is that you can just buy a micro with a real time clock included, but this gave me an excuse to learn I2C. The microcontroller was an arduino, because as far as needing software or fancy programmers they represent an absolute minimum of effort and are acceptable for an application that doesn't have any respectable performance criteria.

For the fanout, eight digital outputs of the microcontroller are used to control all of the nixie tubes; effectively an 8 to 40 expansion as one switch is required to control each digit on each nixie tube. The size of the fanout was really somewhat annoying. The tubes have a comma digit to each side of the number that were left unused in this application. One thing to note is that technically access to all digits in each tube is not required; this was going to be a 24 hour clock making it so that only 3/10 available digits were used on the 10's hours digit...actually you could get away with 2/10 on the last digit if it was blanked instead of showing a '0' which would let you do everything with 32 outputs. But you could definitely do a 12 hour clock with 32 outputs. I'm getting away from crapping on the the current design which should have been implemented as a set of shift registers (or a single shift register). The fanout setup in the current system that was done for the following reasons:

A. to teach someone about human time vs. electrical time.

B. To have them consider the boundaries of what is required vs. what is optimal.

C. For some short amount of time it seemed like a fun idea.

A and B still seem like valid reasons. the fanout was set up as two channels of BCD, 4-digital pins of the micro went to each channel feeding one BCD which then fed 2 more BCDs from its 10 valid outputs. One set of three BCD for the minutes, another set for the hours.

This encoding and conversion was just annoying to deal with. There is one aspect missing here, because the first layer of the fanout can only select one output at a time, it can't produce all the combinations required on the output BCD's. To do this the following circuit was used:

On the input of each second layer BCD the voltage is held by the RC. Then refreshed before the RC runs out. This allows the first layer BCD to turn on an arbitrary set of inputs to the second layer as long as its quick enough, which is pretty easy as long as the RC time constant is long enough. It's dumb but it seemed to work pretty well.

Finally after all these shenanigans the output of each second level BCD goes to a high voltage transistor for switching each digit on the tubes. This whole ordeal was far more trouble than it needed to be. But whatever, the clock clocks, and damn if those glowing tubes don't look pretty.

|

| mmm glowy |

I bought a box to put the clock in as well, because not shocking people is important. That's less exciting, but I might make a post about it.

What's exciting though is I've already started on my next nixie venture and I'm most of the way done with it. It uses it's own silly topology and does not use any switching regulators to run off of the line, so you will be seeing a post about that.

2016-10-30

On Voltage Multipliers, Spiral Multipliers

Of late I have been thinking about voltage multipliers for a variety of reasons. One of which was that I wanted to build a nixie clock and it seemed like an excellent excuse to over design something which could be far simpler. This circuit is what I call a spiral multiplier and I'll get into the details of it in a bit. A friend wanted to learn something about electronics when deciding to do this and this circuit seemed like an interesting way to learn about a variety of concepts and component properties at the same time. The tubes I planned on using could 'just' be powered off of rectified wall voltage with some resistors and filtering, but for safety's sake its nice not to power things with up to 170V and a kW of power oomph. It also makes the problem more interesting stepping the low voltage up to the higher voltage.

I somewhat arbitrarily decided to take 15V and turn it into; $\gt$ 140V at full load (minimum holding voltage of the tubes) to power the nixie tubes. Really the tubes need 170V to spark over according to the data sheet. The decision to go with a multiplier was partly motivated by not being very pleased by many of the transformers I saw available. But realistically speaking using a transformer would be the practical thing to do in this besides powering the tubes off wall power; but where is the fun in that?

Lots of things are technically feasible in this case since it is a low power supply and don't care about the efficiency of a nixie clock as long as heat sinks aren't required.

Which brings about applicable designs and the aforementioned spiral multiplier:

The body of the multiplier (everything on the upper left side of the schematic) is the part pertaining to this post. It is all about the caps and the diodes.

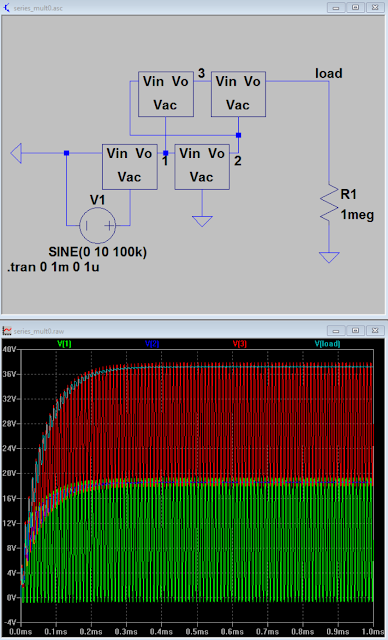

The above traces are for a controlled output set point, if left to its own devices the multiplier will go to a much higher voltage at full power. Open loop the circuit went up to ~200V. The above schematic doesn't look much like a spiral. Below is a topological approximation of the spice simulation circuit which most importantly looks like a spiral:

This spiral topology represents a combo of two basic multiplier types the parallel and series style multipliers. Each 'spoke' coming from the center of the spiral is topologically identical to a capacitor string (or stack) found in a series multiplier while each round of the spiral is analogous to travelling up a parallel multiplier. The spiral multiplier of some arbitrary number of rounds $ \geq 1$ and spokes $ \geq 2$ is a generalization of the series and parallel multipliers where either one represents a base case; spiral circuits similar to the full wave cockcroft-walton multiplier can also be constructed (look at the wikipedia page).

Backing up to the big picture:

Diode based voltage multipliers have been around a very long time like almost a 100ish years according to the wikipedia. If you aren't familiar with voltage multipliers they do as the name implies and take a smaller magnitude (AC) voltage and turn it into a larger magnitude (DC) voltage of some multiple of the AC amplitude (in the ideal case).

Fundamentally multipliers are built up of capacitor coupled nodes with some diodes slapped on. This forms a network of peak detectors, each peak detector takes the peak AC voltage through a diode and deposits it on to a capacitor. This forms a 'unit pump':

In the unit pump, if $Vac$ dips below $Vin$ (by a diode drop), charge is deposited onto capacitor C1. $Vo = Vin-Vd$ when Vac swings positive you get: $\hat{Vo} = \hat{Vac} + Vc$. The capacitor maintains a DC bias from the AC wave form injected through Vac boosting Vo.

These unit pumps are chained in various formats to form different types of multipliers.

Traditional diode multipliers tend to break down into two forms series/cascade multipliers and dickson/parallel multipliers which are generally treated as two fundamentally different approaches.

A series multiplier is driven from a power source a coupled up through all the subsequent stages whereas in a parallel multiplier the power source is directly coupled through a capacitor to a node in a chain of diodes. The difference in the power coupling has interesting effects. The source impedance of a series multiplier increases as the cube of the number of stages; this is an incredible pain sometimes. However it conveniently grades the voltage up the whole multiplier stack so you only have to couple power into the low voltage end and all of your components can be of a lower voltage rating.

A parallel multiplier doesn't have that $n^{3}$ impedance issue but requires direct energy couplings to the high voltage end resulting in a fair amount of energy storage (for the same F capacitors) and it doesn't grade the voltage with the capacitors. Note the similarity between the above series example and the below parallel example

The voltage increases by the Vpp AC voltage with every pumping node and gets filtered to some extent by every filtering node. Both multipliers have the same AC source and reach the similar output voltage.

Both are special in their own way. However both also only represent usage of the unit pump in one 'dimension'. The spiral multiplier is the cross of the two defining a a series/parallel matrix of unit cells. I haven't actually analyzed the topology in detail to see if there are any fundamentally better properties, but it seems like a fun experiment. Analytical awesomeness can be postponed.

Here is an example of a spiral multiplier.It is effectively 2 parallel multipliers (each consisting of 4 unit cells) stacked on top of each other. The output of the lower one feeding the input of the higher voltage one. Really you could string $n$ of them together on top of each other and feed the bias of each multiplier one into the beginning of the next. Alternately it can be seen as taking $M$ series capacitor strings and setting them side by side, linking up each DC biased section in the proper format. 2 rounds of a 4 spoke spiral. How it is viewed is a somewhat arbitrary exercise imo. that could be argued multiple ways depending on the nuances of a particular system. Every circuit is what it does. Note that in the initial 4x3 multiplier at the top of the post I didn't even bother with a filter string in the body of the multiplier, just an output peak detector to mellow the output ripple.

I'm tired of typing about this right now and feel like it'll turn into a thesis if I keep going. The spiral multiplier concept seemed like an interesting one and there are a couple expansions of the topology that I can think of, involving peak detector loops over filter caps and gaming the phasing of the pump sources.

toodloo

I somewhat arbitrarily decided to take 15V and turn it into; $\gt$ 140V at full load (minimum holding voltage of the tubes) to power the nixie tubes. Really the tubes need 170V to spark over according to the data sheet. The decision to go with a multiplier was partly motivated by not being very pleased by many of the transformers I saw available. But realistically speaking using a transformer would be the practical thing to do in this besides powering the tubes off wall power; but where is the fun in that?

Lots of things are technically feasible in this case since it is a low power supply and don't care about the efficiency of a nixie clock as long as heat sinks aren't required.

Which brings about applicable designs and the aforementioned spiral multiplier:

|

| 4 series 3 parallel Spiral Multiplier, peak detector on output as filter. |

|

| Output Voltage green (set a lower control voltage), control feed back: red, pink is the gate voltage on the feed back transistor. |

|

| Spiral style schematic of the nixie multiplier, it has a filtering peak detector on the output. |

This spiral topology represents a combo of two basic multiplier types the parallel and series style multipliers. Each 'spoke' coming from the center of the spiral is topologically identical to a capacitor string (or stack) found in a series multiplier while each round of the spiral is analogous to travelling up a parallel multiplier. The spiral multiplier of some arbitrary number of rounds $ \geq 1$ and spokes $ \geq 2$ is a generalization of the series and parallel multipliers where either one represents a base case; spiral circuits similar to the full wave cockcroft-walton multiplier can also be constructed (look at the wikipedia page).

Backing up to the big picture:

Diode based voltage multipliers have been around a very long time like almost a 100ish years according to the wikipedia. If you aren't familiar with voltage multipliers they do as the name implies and take a smaller magnitude (AC) voltage and turn it into a larger magnitude (DC) voltage of some multiple of the AC amplitude (in the ideal case).

Fundamentally multipliers are built up of capacitor coupled nodes with some diodes slapped on. This forms a network of peak detectors, each peak detector takes the peak AC voltage through a diode and deposits it on to a capacitor. This forms a 'unit pump':

|

| The unit cell of a multiplier |

In the unit pump, if $Vac$ dips below $Vin$ (by a diode drop), charge is deposited onto capacitor C1. $Vo = Vin-Vd$ when Vac swings positive you get: $\hat{Vo} = \hat{Vac} + Vc$. The capacitor maintains a DC bias from the AC wave form injected through Vac boosting Vo.

These unit pumps are chained in various formats to form different types of multipliers.

A series multiplier is driven from a power source a coupled up through all the subsequent stages whereas in a parallel multiplier the power source is directly coupled through a capacitor to a node in a chain of diodes. The difference in the power coupling has interesting effects. The source impedance of a series multiplier increases as the cube of the number of stages; this is an incredible pain sometimes. However it conveniently grades the voltage up the whole multiplier stack so you only have to couple power into the low voltage end and all of your components can be of a lower voltage rating.

|

| Series multiplier, takes 20Vpp input, 40Vmax output |

A parallel multiplier doesn't have that $n^{3}$ impedance issue but requires direct energy couplings to the high voltage end resulting in a fair amount of energy storage (for the same F capacitors) and it doesn't grade the voltage with the capacitors. Note the similarity between the above series example and the below parallel example

|

| Parallel multiplier, takes 20Vpp input, 40Vmax output |

The voltage increases by the Vpp AC voltage with every pumping node and gets filtered to some extent by every filtering node. Both multipliers have the same AC source and reach the similar output voltage.

Both are special in their own way. However both also only represent usage of the unit pump in one 'dimension'. The spiral multiplier is the cross of the two defining a a series/parallel matrix of unit cells. I haven't actually analyzed the topology in detail to see if there are any fundamentally better properties, but it seems like a fun experiment. Analytical awesomeness can be postponed.

|

| A 2x4 Spiral Multiplier |

|

| 2x4 Wave forms with tiny load |

Here is an example of a spiral multiplier.It is effectively 2 parallel multipliers (each consisting of 4 unit cells) stacked on top of each other. The output of the lower one feeding the input of the higher voltage one. Really you could string $n$ of them together on top of each other and feed the bias of each multiplier one into the beginning of the next. Alternately it can be seen as taking $M$ series capacitor strings and setting them side by side, linking up each DC biased section in the proper format. 2 rounds of a 4 spoke spiral. How it is viewed is a somewhat arbitrary exercise imo. that could be argued multiple ways depending on the nuances of a particular system. Every circuit is what it does. Note that in the initial 4x3 multiplier at the top of the post I didn't even bother with a filter string in the body of the multiplier, just an output peak detector to mellow the output ripple.

I'm tired of typing about this right now and feel like it'll turn into a thesis if I keep going. The spiral multiplier concept seemed like an interesting one and there are a couple expansions of the topology that I can think of, involving peak detector loops over filter caps and gaming the phasing of the pump sources.

toodloo

Labels:

multiplier

2015-10-07

The Derp Driver

Everyonce in a while I get a really dumb idea behold the derp drive:

Derp Drive 99% 'what if?', 1% something else

So one day I decided that I wanted to make a cutesy little bench top supply because bench top supplies are balls expensive. I'm going to talk about the rest of this venture at a later date. But today I will talk for too long about the gate drive and how it is for the most part an exercise in curiosity.

Imagine for a moment that you wanted to switch a supply at 500kHz on a full bridge in an odd synchronous fashion. Your are strapped by cash and need synchronous rectification on the output because you're going to be dealing with high current and low voltages. You also want the output floating because if the output floats that's handy it means you can have +V or -V or stacked or paralleled if the outputs can share current.

But doing synchronous rectification requires gate drives, some weird boot strapping some form of isolation. If gate drives go in that means an auxiliary floating set of voltage rails for the drivers and some sort of sensing the voltage state which means chips and rails and money and stuff.

It would be nice if all the switches were driven by floating things, you know kinda like a transformer.

But transformers cost money they are big and slow and inductive... but that is a fallacy. Lots of fast things use transformers for signals, pulse transformers are things, USB uses transformers, ETHERNET uses transformers. Ain't nobody calling my gigabits slow. There are some highly legitimate reasons why signals like usb and ethernet utilize magnetic coupling for signals:

- It can be isolated electrically. My laptop could sit at a completely different potential than your laptop, powered by batteries or off the line and they could still yarble at one another over an CAT5e cable thanks tot he awesomeness that is transformers.

- A local return path/ reference. Any signal sent out needs to be with reference to something and have a return path and to be a fast signal inductance needs to be minimized. This is why PCIe, usb, ethernet, SATA and ect. are all differential pairs for high speed signalling. Transformers by nature create a differential voltage source. As a statement of Gauss's law and conservation of charge they must create a + and relative - to maintain the E field flux but I'm going off on a limb. The important bit is that by creation of a differential signal a return path exists that does not necessarily need to be referenced to ground or anything in particular besides the other end of the wire in the transformer.

- You can have common modes impedance without differential mode impedance. if your output if flapping around a some voltage this can help keep noise from getting into the primary side of the circuit. because transformers aren't perfect and they have some amount of capacitance going from the secondary to primary side.

Transformers are pretty nifty for a variety of reasons, but they have their limitations. That being said in the system of this gate drive I am worried about the volt-seconds that the cores will be able to withstand before saturating.

Once the cores become saturated the primary becomes decoupled from the secondary in at least one direction and the ability to keep the switches in a specific state compromised (to some extent). The ethernet transformers I have seen largely don't come with a primary volt-second spec. However the ethernet transformers I have seen seem to posses a magnetizing inductance of ~300uH which I thought was surprisingly high, and I think puts the idea of the gate driver on the edge of potentially acceptable/ practical.

As far as practical implementations go all of the ethernet transformers are center tapped on the primary and secondary side. By running a push-pull converter using the primary centertap the transformer is a 2:1 step up. This allows you to effectively drive a fet using logic level voltages, once you get above 10V on the gate of a FET the reduction in Rds on is generally marginal. I think the advantage this system would get from running at higher voltages is the faster turn on time of the switch but once the switches are on it won't matter much.

This brings into discussion a few things which I have marginally modeled in spice. What limits the turn on speed of the device? Like I got a voltage source with some impedance. The switches require some base line amount of voltage to turn on. The FET gates are a derpy capacitor, in order to turn on the switch requires some amount of charge slapped on the gate which roughly translates into a given amount of energy (roughly). The goal of a fast gate driver must be to deposit that energy onto the gate as a fast as possible. Any impedance between your roughly ideal voltage source of a decoupling cap which is hopefully sized significantly larger than your gate capacitance otherwise what the fuck are you doing, will restrict the flow of power. There were many many assumptions made in that last sentence.

But what it boils down to is what is throttling the current? resistance or inductance? with a transformer inductance can be a severe issue at high frequency. Even if the fundamental frequency of the switching isn't that fast what is important its about the rise time of the gates voltage waveform. The long the turn on the longer the losses and that what I care about reducing.

But holy fuck the post is longer than I expected and I'm just glossing over things. may I'll post the spice sim next post.

But holy fuck the post is longer than I expected and I'm just glossing over things. may I'll post the spice sim next post.

2015-09-27

On the Mother board and stepper carriers

The mother board I was referring to in my last post got made and seems roughly functional.

Despite me screwing up the stepper driver to some extent.

The mother board should be able to interface to six of the stepper carriers as soon as I produce a stepper carrier that isn't inherently screwed up ...besides the first round of stepper carriers which worked just fine ironically.Tango 1.1.3 has some dumb issues as i turns out not all 780x devices in the same packages have the same pin out and I was playing a bit fast and loose with the foot prints and mixed up the 5V with the ctl power in on the 5V regulator I was using. This may have resulted in burning out the gate driver chip immediately since I wasn't able to coax any PWMing out of the tango driver after fixing the foot print mess up. Le sigh.

Time to populate/kludge another carrier board. If this time round I get the board built up right and touble shoot it it will be pretty exciting to have a board carrier for so many boards. It will make a nice test platform.

The mother board is laid out in a fashion that allows for n arduino mini or some other equivalent micro to be mounted onto the board and have its outputs connect to all the varirious driver boards through the parallel busses laid out on the mother board. There are up to ~8 accessible signals on each bus/ for each driver board (the GND/SIG/GND/SIG/GND/SIG traces reffered to in the last post). This was intended to leave the future possibilities open. Currently the stepper driver would only use 2 signals/ driver leaving lots of possibilities.

Hopefully I'll get something done on the stepper fron again soon. I've been a bit distracted by other electronics and that whole having a job thing.

Despite me screwing up the stepper driver to some extent.

The mother board should be able to interface to six of the stepper carriers as soon as I produce a stepper carrier that isn't inherently screwed up ...besides the first round of stepper carriers which worked just fine ironically.Tango 1.1.3 has some dumb issues as i turns out not all 780x devices in the same packages have the same pin out and I was playing a bit fast and loose with the foot prints and mixed up the 5V with the ctl power in on the 5V regulator I was using. This may have resulted in burning out the gate driver chip immediately since I wasn't able to coax any PWMing out of the tango driver after fixing the foot print mess up. Le sigh.

Time to populate/kludge another carrier board. If this time round I get the board built up right and touble shoot it it will be pretty exciting to have a board carrier for so many boards. It will make a nice test platform.

The mother board is laid out in a fashion that allows for n arduino mini or some other equivalent micro to be mounted onto the board and have its outputs connect to all the varirious driver boards through the parallel busses laid out on the mother board. There are up to ~8 accessible signals on each bus/ for each driver board (the GND/SIG/GND/SIG/GND/SIG traces reffered to in the last post). This was intended to leave the future possibilities open. Currently the stepper driver would only use 2 signals/ driver leaving lots of possibilities.

Hopefully I'll get something done on the stepper fron again soon. I've been a bit distracted by other electronics and that whole having a job thing.

Labels:

millathe

2014-03-16

Motherboard/ Driver carrier board preview

Here is a preview/test route of the motherboard to hold the tango drivers:

The traces go kind of like this:

gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd

I'll talk about why in my next post and some adjustments I made to the tango board before sending it to the fab, I need sleep.

The traces go kind of like this:

gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd, signal, gnd

I'll talk about why in my next post and some adjustments I made to the tango board before sending it to the fab, I need sleep.

2014-03-04

Stepper Driver v1.1.3: tango: ready for manufacturing

So the next iteration of the stepper driver for the millathe has been laid out. It it fixes a few quirks on the waltz board such as some mussed up foot prints and lack of labelling on the dip switches. Also it takes up much less copper are and uses a different card edge connector, actually made to fit a 64 pin PCIe connector. Why? Because as it turns out PCIe connectors are

1. apparently way cheaper than other car edge connectors mostly likely because they're made in stupid quantities.

2. capable of carrying fairly high currents 1A+/pin*64 pins = more amps than a board this size should carry.

3. It's metric and has a 1mm pin pitch, the 1mm pitch is nice and small shrinking the space the signals take up vs .1" pitch. Also I abhore standard units and .1" spacing is the bane of my existance.

4. A 2x32 pin connector is just about the right size for this board.

That being said lets take a look at this board, behold Tango:

You might have noticed I did not skimp on the copper. all of the large current carrying traces (motor voltage, pwrgnd, all motor out/inputs) are straight up polygons. I figured there really was no harm in increasing the power sinking capabilities of the board. Actually there is some harm assembly will be slightly more painful, there are no thermals on this board, it is made to be soldered in an oven or with the aid of a hot air gun. The terminal connectors on the left hand side of the board just won't go on with out the soldering iron turned to the max other wise. However besides that one downside there isn't much of a case against using all of the power side copper that is is available in this scenario. I would rather maximise dissipative capabilities and minimize dissipation.

As far as gate driving is concerned this circuit is still using the original A4989 output as the driver despite (in my opinion) it's relative low current output in the 10's to -barley 100's of mA range for maybe a 20Ohmish resistive values on the gate output. One this I might want to experiment with in this scenario is the ringing effects of an under damped gate vs. the losses from turning on slower due to the damped circuit. In order to minimize inductance ( and therefore overshoot/ringing) in the system each gate drive trace was routed in a pair with a trace going to the source of it's corresponding mosfet, similar to a parallel port matching each signal is matched with a return ground for lower inductance. With the smaller loop it will also lower noise from inductive coupling from the currents on the power side of the board.

In comparison with the last stepper board this one boasts a larger volume pair of decoupling caps for the motors, they could probably be smaller and they take up an ass load of room where assload is like 1cm^2 each... maybe not huge but for this board that is a big component. If you put a rectangle arround the board there is around 35cm^2 of area on this board making them take up around roughly 5.7% of all possible physical space.

But on the plus side with the increased size of the capacitors allows me to use ones with higher voltage ratings/ capacitance ratings. That was a major limiting factor of the driver last time. Now the main voltage limitation is the power mostfets.

So about them

mosfets. this time around going with the DPAK FDD8778 again same fet as last time. One of the main reasons I'm going with it again is it's relatively low gate charge and reasonable on resistance (14mOhm@25C/10vgs). When operating at higher voltages my calculations say that according to the equation:

\\[ Psw = I_{ds} V_{ds} /2(Q/ I_{hl} +Q) \\

but apparent the latex add in I have isnt working... I'll edit this bit later.

Either way the important take away is this equation:

Psw = Ids*Vds/2*Qg*(1/ihl+1/ilh)

It represents the switching power losses occuring in the system.

As far as numbers go for me.

Vds=25V

Ids = 10A

Qg(that I care about) ~ 9nC

ihl/ilh~100mA with a complete short on the driver (I'm going to look at how low a value of gate resistors this circuit can get away with)

f=some weird poop

Now the stepper frequency, it has a linear correlation with your switching losses and is therefore important highly dependent on your control method. In the tango driver, the A4989 controller provides a hysteretic-constant off time current control method. A hysteretic controllers are also called bang-bang controllers, they are not constant frequency and the dependent on the system load. Often thermostats contol temperature using a bang-bang controller. Generally with a hysteretic controller you have a high limit and a low limit, when the output sense is below the lower limit the controller turns on the power full blast, then once the out put sense reaches the higher limit it turns off the power.

Example:

Your thermostat is set to 70 with +/-5 degree limits on the temperature, the temperature is dropping in your house because it's winter and cold outside. The temperature in your house drops to 65. The thermostat senses this and cranks on the heater; depending how large your house is and how powerful the heater affects how quickly your house heats up. Regardless of how long it takes, your heater is going to try it's damnedest to heat up that house as fast as it possibly can. Once your house is 75 degree the thermostat shuts off the the heater and your house begins to cool again. This cycle then repeats.

In the control of the stepper motor the controller is similar, but rather than having a lower limit it just turns the controller off for a fixed time. With this controller, the controller clock is 4MHz (set through a resistor) and the fixed off time is 87 clock cycles. This sets an upper limit pwm frequency of ~46kHz, giving us a decay time of 21.75microseconds. The load dynamics decide how long the on-period will be. The load: a big ass stepper motor, motors are commonly modeled as a voltage source, inductor and resistor. What matters most in this case is this motor inductance.

For a decay time of 21.75us assuming we are dominated by the motor inductance... the time constant is 2.8mH/.73Ohm = millisecond range = way longer than we care about (go on wikipedia and read about RC and L/R time constants if you are curious). Assuming steady state operation with the stepper motor which is ironically is a pretty bad case for this controller in terms of power dissipation, but that is another interesting discussion that is highly related but I don't want to get into right now.

If the motor is drawing 5A RMS on a phase

dIon=dIoff

Von*dton/L=Voff*dtoff/L

dton=Voff*dtoff/Von

You know what, maximum pwm frequency in the steady state is 35ish kHz and I'm tired of writing about this right now this post really went on a tangent. More about controls pwm frequency and losses later and how it relates to this controller.

Either way the drivers should have pretty much the same amperage rating as the last ones at (+10A) but with more voltage up to 25V till the fets poop them selves giving it 200W/ driver minimum for a bit of margin on the driving voltage, I'll be on the look out to better suited fets to increase the power density of the system since that is a real limiting factor at the moment.

I'm gonna go order the boards now.

1. apparently way cheaper than other car edge connectors mostly likely because they're made in stupid quantities.

2. capable of carrying fairly high currents 1A+/pin*64 pins = more amps than a board this size should carry.

3. It's metric and has a 1mm pin pitch, the 1mm pitch is nice and small shrinking the space the signals take up vs .1" pitch. Also I abhore standard units and .1" spacing is the bane of my existance.

4. A 2x32 pin connector is just about the right size for this board.

That being said lets take a look at this board, behold Tango:

|

| Top + bottom |

|

| top |

|

| bottom |

As far as gate driving is concerned this circuit is still using the original A4989 output as the driver despite (in my opinion) it's relative low current output in the 10's to -barley 100's of mA range for maybe a 20Ohmish resistive values on the gate output. One this I might want to experiment with in this scenario is the ringing effects of an under damped gate vs. the losses from turning on slower due to the damped circuit. In order to minimize inductance ( and therefore overshoot/ringing) in the system each gate drive trace was routed in a pair with a trace going to the source of it's corresponding mosfet, similar to a parallel port matching each signal is matched with a return ground for lower inductance. With the smaller loop it will also lower noise from inductive coupling from the currents on the power side of the board.

In comparison with the last stepper board this one boasts a larger volume pair of decoupling caps for the motors, they could probably be smaller and they take up an ass load of room where assload is like 1cm^2 each... maybe not huge but for this board that is a big component. If you put a rectangle arround the board there is around 35cm^2 of area on this board making them take up around roughly 5.7% of all possible physical space.

But on the plus side with the increased size of the capacitors allows me to use ones with higher voltage ratings/ capacitance ratings. That was a major limiting factor of the driver last time. Now the main voltage limitation is the power mostfets.

So about them

mosfets. this time around going with the DPAK FDD8778 again same fet as last time. One of the main reasons I'm going with it again is it's relatively low gate charge and reasonable on resistance (14mOhm@25C/10vgs). When operating at higher voltages my calculations say that according to the equation:

\\[ Psw = I_{ds} V_{ds} /2(Q/ I_{hl} +Q) \\

but apparent the latex add in I have isnt working... I'll edit this bit later.

Either way the important take away is this equation:

Psw = Ids*Vds/2*Qg*(1/ihl+1/ilh)

It represents the switching power losses occuring in the system.

As far as numbers go for me.

Vds=25V

Ids = 10A

Qg(that I care about) ~ 9nC

ihl/ilh~100mA with a complete short on the driver (I'm going to look at how low a value of gate resistors this circuit can get away with)

f=some weird poop

Now the stepper frequency, it has a linear correlation with your switching losses and is therefore important highly dependent on your control method. In the tango driver, the A4989 controller provides a hysteretic-constant off time current control method. A hysteretic controllers are also called bang-bang controllers, they are not constant frequency and the dependent on the system load. Often thermostats contol temperature using a bang-bang controller. Generally with a hysteretic controller you have a high limit and a low limit, when the output sense is below the lower limit the controller turns on the power full blast, then once the out put sense reaches the higher limit it turns off the power.

Example:

Your thermostat is set to 70 with +/-5 degree limits on the temperature, the temperature is dropping in your house because it's winter and cold outside. The temperature in your house drops to 65. The thermostat senses this and cranks on the heater; depending how large your house is and how powerful the heater affects how quickly your house heats up. Regardless of how long it takes, your heater is going to try it's damnedest to heat up that house as fast as it possibly can. Once your house is 75 degree the thermostat shuts off the the heater and your house begins to cool again. This cycle then repeats.

In the control of the stepper motor the controller is similar, but rather than having a lower limit it just turns the controller off for a fixed time. With this controller, the controller clock is 4MHz (set through a resistor) and the fixed off time is 87 clock cycles. This sets an upper limit pwm frequency of ~46kHz, giving us a decay time of 21.75microseconds. The load dynamics decide how long the on-period will be. The load: a big ass stepper motor, motors are commonly modeled as a voltage source, inductor and resistor. What matters most in this case is this motor inductance.

For a decay time of 21.75us assuming we are dominated by the motor inductance... the time constant is 2.8mH/.73Ohm = millisecond range = way longer than we care about (go on wikipedia and read about RC and L/R time constants if you are curious). Assuming steady state operation with the stepper motor which is ironically is a pretty bad case for this controller in terms of power dissipation, but that is another interesting discussion that is highly related but I don't want to get into right now.

If the motor is drawing 5A RMS on a phase

dIon=dIoff

Von*dton/L=Voff*dtoff/L

dton=Voff*dtoff/Von

You know what, maximum pwm frequency in the steady state is 35ish kHz and I'm tired of writing about this right now this post really went on a tangent. More about controls pwm frequency and losses later and how it relates to this controller.

Either way the drivers should have pretty much the same amperage rating as the last ones at (+10A) but with more voltage up to 25V till the fets poop them selves giving it 200W/ driver minimum for a bit of margin on the driving voltage, I'll be on the look out to better suited fets to increase the power density of the system since that is a real limiting factor at the moment.

I'm gonna go order the boards now.

Subscribe to:

Posts (Atom)